|                                                                       | Reg. No.                                                                                                                                                    |                                                             |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|                                                                       | Question Paper Code12552                                                                                                                                    |                                                             |

| B.E. / B.Tech - DEGREE EXAMINATIONS, NOV / DEC 2023<br>Third Semester |                                                                                                                                                             |                                                             |

| <b>Computer and Communication Engineering</b>                         |                                                                                                                                                             |                                                             |

| 20CCPC301 - DIGITAL LOGICS AND SYSTEM DESIGN<br>(Regulations 2020)    |                                                                                                                                                             |                                                             |

| Dur                                                                   |                                                                                                                                                             | larks: 100                                                  |

| PART - A (10 × 2 = 20 Marks)<br>Answer ALL Questions                  |                                                                                                                                                             |                                                             |

| 1.                                                                    | State the Features of ECL.                                                                                                                                  | Marks,<br>K-Level, CO<br>2,K1,CO1                           |

| 2.<br>3.                                                              | Infer how conversion of 0.6875, decimal value to Octal & Binary occurs? State the difference between Demux and Decoder.                                     | 2,K2,CO1<br>2,K1,CO2                                        |

| 4.                                                                    | Infer the following Boolean function using 8:1 multiplex $F(A,B,C)=\sum(1,3,5,6)$ .                                                                         | er 2,K2,CO2                                                 |

| 5.                                                                    | Define Flow Table.                                                                                                                                          | 2,K1,CO4                                                    |

| 6.                                                                    | Identify, what is the minimum number of Flip Flops required to design counter of modulo 60?                                                                 | a 2,K2,CO4                                                  |

| 7.                                                                    | Distinguish between Critical and Non critical Races.                                                                                                        | 2,K2,CO5                                                    |

| 8.                                                                    | Outline the steps for the design of asynchronous sequential circuit.                                                                                        | 2,K2,CO5                                                    |

| 9.                                                                    | What is memory decoding?                                                                                                                                    | 2,K1,CO6                                                    |

| 10.                                                                   | Distinguish between PAL, PLA and PROM.                                                                                                                      | 2,K2,CO6                                                    |

|                                                                       | PART - B (5 × 13 = 65 Marks)<br>Answer ALL Questions                                                                                                        |                                                             |

| 11.                                                                   | <ul> <li>a) Explain the working principle of Hamming Code with an example State its advantages over parity codes.</li> <li>OR</li> </ul>                    | le. 13,K2,CO1                                               |

|                                                                       | b) Write short notes on<br>(i) RTL<br>(ii) ECL                                                                                                              | 13,K1,CO1                                                   |

| 12.                                                                   | a) Implement a staircase light, which is controlled by two-way switched<br>one is at the top of the stairs and the other is at the bottom of the<br>stairs. |                                                             |

|                                                                       | (i) Make a truth table for this system.                                                                                                                     | 3,K3,CO2                                                    |

|                                                                       | (ii) Write the logic function in SOP form.                                                                                                                  | 3,K3,CO2                                                    |

|                                                                       | <ul><li>(iii) Realize the circuit using basic logic gates.</li><li>(iv) Realize the circuit using minimum number of NAND and NC gates.</li></ul>            | 3, <i>K</i> 3, <i>C</i> 02<br>DR 4, <i>K</i> 3, <i>C</i> 02 |

|                                                                       | 0                                                                                                                                                           |                                                             |

K1 – Remember; K2 – Understand; K3 – Apply; K4 – Analyze; K5 – Evaluate; K6 – Create 12552

## OR

- b) Construct the BCD code to Excess 3 code with neat logical diagram. 13,K3,CO2

- 13. a) Outline a sequential circuit for a given state diagram, use state <sup>13,K2,CO4</sup> reduction if necessary and also use D flip-flop and give what is the aim of Set reduction?

- b) Explain the universal shift registers with neat diagram. 13,K2,CO4

- 14. a) (i) What is a Hazard? Give hazard free realization for the following  $^{9,K2,CO5}$ Boolean function. F (A, B, C, D) =  $\sum m$  (1,5,6,7) using AND- OR gate network.

- (ii) Define Essential Hazards with an example. 4,K1,C05

### OR

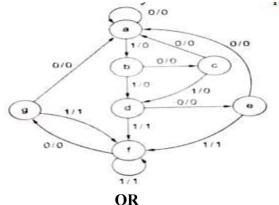

- b) Illustrate the design an asynchronous sequential circuit with inputs x1 <sup>13,K2,C05</sup> and x2 and one output z. Initially and at any time if both the inputs are 0, output is equal to 0. When x1 or x2 becomes 1, z becomes 1. When second input also becomes 1, z=0; the output stays at 0 until circuit goes back to initial state.

- 15. a) Explain how a BCD to Excess-3 code converter designed and <sup>13,K2,CO6</sup> implement the same using suitable PLA.

### OR

b) (i) Illustrate the following Boolean functions using 8 x 2 PROM. F1=  $^{6,K2,CO6}$  $\Sigma m (3,5,6,7)$  and F2= $\Sigma m (1,2,3,4)$ .

(ii) Implement the following Boolean functions using PLA with 3 <sup>7,K2,CO6</sup> inputs, 4 product terms and 2 outputs. F1=  $\sum m(3,5,6,7)$  and F2=  $\sum m(1,2,3,4)$ .

# PART - C $(1 \times 15 = 15 \text{ Marks})$

16. a) Develop a verilog program for Full Subtractor and explain its timing <sup>15,K3,CO3</sup> diagram waveform.

### OR

b) Design a verilog HDL code for 4x1 MUX and 1x4 DEMUX. 15,K3,CO3

....