|                                                      |                                                                  |                                                         | Reg. No.       |         |         |                 |               |            |  |  |  |

|------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------|----------------|---------|---------|-----------------|---------------|------------|--|--|--|

|                                                      |                                                                  | Question Paper Code                                     | 12695          | 5       |         |                 |               |            |  |  |  |

| M.E. / M.Tech DEGREE EXAMINATIONS, APRIL / MAY 2024  |                                                                  |                                                         |                |         |         |                 |               |            |  |  |  |

| First Semester                                       |                                                                  |                                                         |                |         |         |                 |               |            |  |  |  |

| M.E - Embedded Systems Technologies                  |                                                                  |                                                         |                |         |         |                 |               |            |  |  |  |

| 20PESPC101 - ADVANCED DIGITAL PRINCIPLES AND DESIGN  |                                                                  |                                                         |                |         |         |                 |               |            |  |  |  |

| Regulations - 2020                                   |                                                                  |                                                         |                |         |         |                 |               |            |  |  |  |

| Duration: 3 Hours                                    |                                                                  |                                                         |                |         |         | Max. Marks: 100 |               |            |  |  |  |

| PART - A (10 × 2 = 20 Marks)<br>Answer ALL Questions |                                                                  |                                                         |                |         |         | Mark            | K–<br>S Level | CO         |  |  |  |

| 1.                                                   | 1. Distinguish Synchronous and Asynchronous sequential circuits. |                                                         |                |         |         |                 | K2            | <i>CO1</i> |  |  |  |

| 2.                                                   | 2. Enumerate the elements present in ASM chart.                  |                                                         |                |         |         | 2               | K2            | <i>CO1</i> |  |  |  |

| 3.                                                   | . What do you meant by race around condition?                    |                                                         |                |         |         | 2               | K1            | <i>CO2</i> |  |  |  |

| 4.                                                   | . What is an essential hazard?                                   |                                                         |                |         |         | 2               | K2            | <i>CO2</i> |  |  |  |

| 5.                                                   | 5. How is Fault Simulation used in testing?                      |                                                         |                |         |         | 2               | K1            | СО3        |  |  |  |

| 6. Define defect, error and fault.                   |                                                                  |                                                         |                |         |         | 2               | K2            | СО3        |  |  |  |

| 7.                                                   | 7. List the features of FPGA.                                    |                                                         |                |         |         | 2               | K1            | <i>CO4</i> |  |  |  |

| 8.                                                   | 8. What is EPLD?                                                 |                                                         |                |         |         | 2               | K2            | <i>CO4</i> |  |  |  |

| 9.                                                   | . Write the structure of the entity in VHDL.                     |                                                         |                |         |         | 2               | K1            | CO5        |  |  |  |

| 10.                                                  | Mention any two op                                               | erators used in VHDL.                                   |                |         |         | 2               | K2            | CO5        |  |  |  |

| PART - B (5 × 13 = 65 Marks)<br>Answer ALL Questions |                                                                  |                                                         |                |         |         |                 |               |            |  |  |  |

| 11.                                                  | ,                                                                | table assignment and rec<br>uits with an example.<br>OR | luction of clo | ocked s | ynchroi | nous 13         | K2            | CO1        |  |  |  |

| b) | Draw the ASM chart for binary multiplier. | 13 | K2 | <i>CO1</i> |

|----|-------------------------------------------|----|----|------------|

|----|-------------------------------------------|----|----|------------|

12. a) Design an Asynchronous sequential circuit with input A and B and an <sup>13</sup> K<sup>3</sup> CO2 output Y. Initially at any time if both the inputs are 0, the output, Y=0. When A or B = 1, Y =1. When the other input also become 1, Y=0. The output stays at 0 until circuit goes back to initial state.

## OR

b) Illustrate about different hazards that occur in sequential circuits and <sup>13</sup> K<sup>2</sup> CO<sup>2</sup> also about the way to eliminate them.

13. a) Describe any one path sensitization method of ATPGs with a suitable <sup>13</sup> K<sup>2</sup> CO3 example.

OR

- b) Generate the test vector and signature analysis for the circuit under test <sup>13</sup> K<sup>2</sup> CO<sup>3</sup> using BIST algorithm.

- 14. a) Explain about the structure of Xilinx 2000 CLB and IO units with neat <sup>13</sup> K<sup>2</sup> CO<sup>4</sup> diagram.

OR

- b) Using PALs, determine the circuit used to realize the following <sup>13</sup> K<sup>2</sup> CO4 Boolean functions.

(i) W(A,B,C,D) = ∑ (0,2, 6,7,8,9,12,13)

(ii) X(A,B,C,D) = ∑ (0, 2, 6, 7, 8, 9, 12, 13, 14)

(iii)Y(A, B, C, D) = ∑ ( 2, 3, 8, 9, 10, 12, 13)

- 15. a) What is Gate level modelling? Explain with a suitable example. 13 K2 CO5 OR

- b) Write a VHDL program for 4:1 multiplexer. 13 K2 CO5

## PART - C $(1 \times 15 = 15 \text{ Marks})$

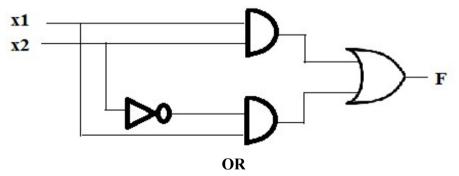

16. a) For the circuit shown below, obtain the Boolean difference with <sup>15</sup> K3 CO3 respect to x2.

b) Describe about ripple carry adder and model it with VHDL code. <sup>15</sup> K3 CO5