| Reg. No. |  |  |  |  |  |  |  |  |

|----------|--|--|--|--|--|--|--|--|

**Question Paper Code**

13556

## B.E. / B.Tech. - DEGREE EXAMINATIONS, APRIL / MAY 2025

Third Semester

## **Electrical and Electronics Engineering**

## 20EEPC304 - DIGITAL LOGIC CIRCUITS

Regulations - 2020

|     | Regulations 2020                                                                       |        |            |     |  |  |  |

|-----|----------------------------------------------------------------------------------------|--------|------------|-----|--|--|--|

| Du  | ration: 3 Hours Ma                                                                     | ax. Ma | ırks:      | 100 |  |  |  |

|     | $PART - A (MCQ) (10 \times 1 = 10 Marks)$                                              | Marks  | <i>K</i> – | co  |  |  |  |

|     | Answer ALL Questions                                                                   | muns   | Level      | CO  |  |  |  |

| 1.  | Identify which error detection method can detect and correct single-bit errors?        | 1      | K2         | CO1 |  |  |  |

|     | (a) Parity Check (b) Hamming Code                                                      |        |            |     |  |  |  |

|     | (c) Check Sum (d) CRC                                                                  |        |            |     |  |  |  |

| 2.  | Which digital logic family is the fastest in terms of switching speed?                 | 1      | <i>K1</i>  | CO1 |  |  |  |

|     | (a) RTL (b) TTL (c) DTL (d) ECL                                                        |        |            |     |  |  |  |

| 3.  | Minimum number of 2:1 multiplexer required to design 16:1 multiplexer is               | 1      | <i>K</i> 2 | CO2 |  |  |  |

|     | (a) 8 (b) 4 (c) 15 (d) 9                                                               |        |            |     |  |  |  |

| 4.  | Choose the correct identity in the following Boolean expression                        | 1      | K2         | CO2 |  |  |  |

|     | (a) $A.\overline{A} = 1$ (b) $A+AB = A+B$ (c) $A(A+B) = B$ (d) $A+\overline{A}B = A+B$ |        |            |     |  |  |  |

| 5.  | Number of Flip flops required for designing synchronous counter having 5 states with   | 1      | K2         | CO3 |  |  |  |

|     | counting sequence: $0 = > 1 = > 6 = > 10 = > 4$ will be:                               |        |            |     |  |  |  |

|     | (a) 5 (b) 4 (c) 3 (d) 9                                                                |        |            |     |  |  |  |

| 6.  | D flip flop can be made from a J-K flip flop by making                                 | 1      | K1         | CO3 |  |  |  |

|     | (a) $J = K$ (b) $J = K = 1$ (c) $J = 0, K = 1$ (d) $J = \overline{K}$                  |        |            |     |  |  |  |

| 7.  | The table that is not a part of the asynchronous analysis procedure is                 | 1      | <i>K1</i>  | CO4 |  |  |  |

|     | (a) Transition Table (b) State Table (c) Flow Table (d) Excitation Table               |        |            |     |  |  |  |

| 8.  | In the asynchronous circuit, the changes occur with the change of                      | 1      | <i>K1</i>  | CO4 |  |  |  |

|     | (a) Input (b) Output (c) Clock Pulse (d) Time                                          |        |            |     |  |  |  |

| 9.  | An Antifuse programming technology is associated with                                  | 1      | <i>K1</i>  | CO5 |  |  |  |

|     | (a) ASIC (b) CPLD (c)SPLD (d) FPGA                                                     |        |            |     |  |  |  |

| 10. | The difference between a PLA and a PAL is:                                             | 1      | K2         | CO5 |  |  |  |

|     | (a) The PLA has a programmable OR plane and a programmable AND plane, while the        |        |            |     |  |  |  |

|     | PAL only has a programmable AND plane.                                                 |        |            |     |  |  |  |

|     | (b) The PAL has a programmable OR plane and a programmable AND plane, while the        |        |            |     |  |  |  |

|     | PLA only has a programmable AND plane.                                                 |        |            |     |  |  |  |

|     | (c) The PAL has more possible product terms than the PLA.                              |        |            |     |  |  |  |

|     | (d) PALs and PLAs are the same thing.                                                  |        |            |     |  |  |  |

|     | $PART - B (12 \times 2 = 24 Marks)$                                                    |        |            |     |  |  |  |

|     | Answer ALL Questions                                                                   |        |            |     |  |  |  |

| 11. | Convert the following number $(3AF)_{16}$ into binary.                                 | 2      |            | CO1 |  |  |  |

| 12. | Apply De-Morgan's theorem to simplify (A'+ BC')'.                                      | 2      | <i>K</i> 2 | CO1 |  |  |  |

| 13. | Identify a suitable logic family for high-speed applications and justify your choice.  | 2      | K2         | CO1 |  |  |  |

| 14. | Implement the given Boolean equation $F = AB + A'B$ using NAND gate.                   | 2      | K2         | CO2 |  |  |  |

| 15. | Modify the Boolean expression $A+BC$ into standard SOP form.                           | 2      | K2         | CO2 |  |  |  |

| 16. | Design a full adder using two half adders and an OR gate.                              | 2      | K2         | CO2 |  |  |  |

| 17. | Differentiate between Moore and Mealey machine.                                        | 2      | K2         | CO3 |  |  |  |

| 18. | Write short note on edge triggering and level triggering.                              | 2      | <i>K1</i>  | CO3 |  |  |  |

| 19. | Outline the concept of static-0 and static-1 hazard.                                   | 2      | K1         | CO4 |  |  |  |

| 20. | <del>-</del>                                                                           | 2      | K2         | CO4 |  |  |  |

| 21. | Write a VHDL code for NAND gate using structural modelling.                            | 2      | <i>K1</i>  | CO5 |  |  |  |

|     |                                                                                        |        |            |     |  |  |  |

| V1  | Pamambar, V2 Understand, V2 Apply, VA Analyzo, V5 Evaluate, V6 Create                  |        | 135        | 56  |  |  |  |

22. Distinguish between volatile and non-volatile memory.

2 K2 CO5

## $PART - C (6 \times 11 = 66 Marks)$

**Answer ALL Questions**

- 23. a) i) Compare the characteristics of RTL, TTL, ECL and CMOS logic families. 7 K2 COI

- ii) Convert the given (A3BF)<sub>16</sub> in to equivalent binary and octal numbers.

- 4 K3 CO1

- OR

- b) i) A 7-bit data word 1011001 is transmitted with an even parity bit. If the received word is 1011101, determine whether an error has occurred. How can Hamming code be used to correct this error?

- ii) Design a NAND gate using TTL logic family.

K3 CO1

5

K2 CO1

- 24. a) i) Minimize the logic function using K-Map. F (A, B, C, D) =  $\Sigma$ m (1,3,5,8,9,11,15) +  $^6$   $^{K3}$   $^{CO2}$   $\Sigma$ d (2,13). Implement the minimal Boolean function using basic gates.

- ii) Design and implement half subtractor circuits with the help of its truth table and 5 K3 CO2 Boolean function.

OR

- b) i) Formulate the following Boolean function using 4 x 1 multiplexers. 4 K3 CO2  $F(A,B,C,D) = \Sigma m (1,2,3,6,7,8,11,12,14)$

- ii) Develop the truth table and implement a logic circuit for binary to gray code 7 K3 CO2 conversion.

- 25. a) i) Explain the working of shift register with a neat sketch.

5 K2 CO3

- ii) Design a Mod 3 synchronous counter using D-FF with its state table, state diagram, 6 K2 CO3 K-map and Logic diagram.

OR

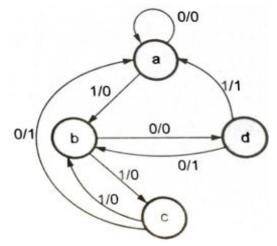

b) Design and implement a clocked sequential circuit using JK flip-flops for the 11 K3 CO3 following state diagram.

26. a) An asynchronous sequential circuit has two internal states and one output. The 11 K3 CO4 excitation and output function describing the circuit are as follows:

$$Y_1 = X_1X_2 + X_1Y_2' + X_2'Y_1$$

$$Y_2 = X_{2+}X_1Y_1Y_2+X_1Y_1$$

$$Z = X_2 + Y_1$$

Draw the logic diagram of the circuits.

- (i) Derive the transition table and output map.

- (ii) Obtain a flow table for the circuit.

OR

b) Design an asynchronous sequential circuit with two inputs (X, Y) and one output <sup>11</sup> <sup>K3</sup> <sup>CO4</sup> (Z), where the output is high only when the input sequence XY = 10 is received in fundamental mode. Draw the state diagram, transition table, and logic diagram.

| 27.     | a) i) | Explain the concept of operators and its types in detail.                       | 6  | <i>K</i> 2 | CO5 |

|---------|-------|---------------------------------------------------------------------------------|----|------------|-----|

|         | ii)   | Draw a PLA circuit to implement the following function.                         | 5  | <i>K</i> 2 | CO5 |

|         |       | F1 = A'B+AC+A'BC'                                                               |    |            |     |

|         |       | F2 = AB + AC + BC                                                               |    |            |     |

|         |       | OR                                                                              |    |            |     |

|         | b)    | Design a 4-bit synchronous up-counter using VHDL. The counter should increment  | 11 | <i>K3</i>  | CO5 |

|         |       | on each rising edge of the clock (CLK) and reset to 0 when the RESET signal is  |    |            |     |

|         |       | high. Also, include an enable input (EN) which allows counting only when        |    |            |     |

|         |       | asserted. Provide the VHDL code.                                                |    |            |     |

| 28.     | a) i) | Describe the steps involved in the design of Asynchronous sequential circuit in | 7  | К3         | CO4 |

| 20. a). | α) 1) | detail with an example.                                                         |    |            |     |

|         | ii)   | Write a VHDL code to evaluate the functionality of full adder using behavioral  | 4  | <i>K</i> 2 | CO5 |

|         | /     | modelling.                                                                      |    |            |     |

|         |       | OR                                                                              |    |            |     |

|         | b) i) | Design hazard free circuit for the following:                                   | 6  | <i>K3</i>  | CO4 |

|         |       | i) $F(A,B,C,D)=\sum (2,5,6,7,10,13,15)$                                         |    |            |     |

|         |       | ii) $F(A,B,C) = \sum (1,3,6,7)$                                                 |    |            |     |

|         | ii)   | Design a 4-to-1 multiplexer in VHDL using RTL design style.                     | 5  | <i>K</i> 2 | CO5 |