|    |                                                                  |                                                       |              | Re          | g. No.     |         |        |      |       |      |      |       |                                  |

|----|------------------------------------------------------------------|-------------------------------------------------------|--------------|-------------|------------|---------|--------|------|-------|------|------|-------|----------------------------------|

|    |                                                                  | Qu                                                    | 12.          | 317         |            |         |        |      |       |      |      |       |                                  |

|    | M.E                                                              | . / M.Tech                                            | DEGRI        | EE EXAM     | IINATIO    | NS, N   | IOV    | / [  | DEC   | 202  | 23   |       |                                  |

|    |                                                                  |                                                       |              | First Sem   | ester      |         |        |      |       |      |      |       |                                  |

|    |                                                                  | <b>M.</b> ]                                           | E Embee      | dded Syste  | ems Tech   | nolog   | ies    |      |       |      |      |       |                                  |

|    | 20PESP                                                           | C101 - AI                                             | VANCEI       | ) DIGITA    | L PRINC    | CIPLE   | ES A   | NI   | ) DE  | SI   | GN   |       |                                  |

|    |                                                                  |                                                       | (R           | egulations  | 2020)      |         |        |      |       |      |      |       |                                  |

| Du | ration: 3 Hou                                                    | ırs                                                   |              | -           |            |         |        |      | Ma    | x. 1 | Mark | cs: 1 | 00                               |

|    |                                                                  |                                                       | PART -       | A (10 × 2   | = 20 Mai   | ·ks)    |        |      |       |      |      |       |                                  |

|    |                                                                  |                                                       |              | wer ALL Q   |            | ,       |        |      |       |      |      |       |                                  |

| 1. | Pagallagt f                                                      | ha Charaot                                            | oristic cau  | ation and t | obla of Ik | flint   | flon   |      |       |      |      | K-Le  | <b>larks</b> ,<br>evel,<br>(1,CC |

|    | Recollect the Characteristic equation and table of JK flip flop. |                                                       |              |             |            |         |        |      |       |      |      | ,     | ,<br>,                           |

| 2. |                                                                  | Recall the excitation table for JK flipflop. $2,KI,C$ |              |             |            |         |        |      |       |      |      |       |                                  |

| 3. | Bring out t                                                      | he importa                                            | nce of state | e reductior | 1.         |         |        |      |       |      |      | 2,K   | (2,CC                            |

| 4. | Give the minimizing                                              | reduced s<br>g the hardw                              |              | in the d    | esign of   | seque   | entia  | 1 c  | ircui | ts   | for  | 2,K   | 2,CC                             |

|    |                                                                  | Present                                               | Next         | Next        | Output     | Out     | tputz  | ,2   |       |      |      |       |                                  |

|    |                                                                  | state                                                 | state        | state       | Z1         | 0 u     | -p atz |      |       |      |      |       |                                  |

|    |                                                                  | a                                                     | d            | b           | 0          |         | 0      |      |       |      |      |       |                                  |

|    |                                                                  | b                                                     | e            | a           | 0          |         | 0      |      |       |      |      |       |                                  |

|    |                                                                  | с                                                     | g            | f           | 0          |         | 1      |      |       |      |      |       |                                  |

|    |                                                                  | d                                                     | a            | d           | 1          |         | 0      |      |       |      |      |       |                                  |

|    |                                                                  | e                                                     | а            | b           | 1          |         | 0      |      |       |      |      |       |                                  |

|    |                                                                  | f                                                     | d            | b           | 0          |         | 0      |      |       |      |      |       |                                  |

|    |                                                                  | g                                                     | а            | e           | 1          |         | 0      |      |       |      |      |       |                                  |

| 5  | Bring out t                                                      | he differen                                           | ce hetweet   | n the stuck | at 0 and   | stuck ( | at 1 f | fami | lt .  |      |      | 2.K   | 2.CC                             |

| 5.  | Bring out the difference between the stuck at 0 and stuck at 1 fault. | 2,K2,CO3 |

|-----|-----------------------------------------------------------------------|----------|

| 6.  | State the importance of Built in Self Test.                           | 2,K1,CO3 |

| 7.  | Differentiate between PAL and PLA.                                    | 2,K2,CO4 |

| 8.  | List the important features of Xilinx FPGA family.                    | 2,K1,CO4 |

| 9.  | Outline the advantage of reconfigurable logic designs.                | 2,K2,CO5 |

| 10. | State the advantages of CLBs.                                         | 2,K1,CO5 |

# PART - B $(5 \times 13 = 65 \text{ Marks})$

Answer ALL Questions

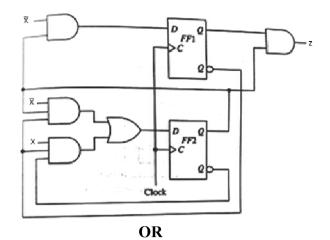

11. a) Illustrate the Transition table, Excitation table, state table and state <sup>13,K2,CO1</sup> diagram for the following synchronous sequential circuit and

- b) An Asynchronous sequential circuit is given by the following excitation and output function  $Y1 = x_1x_2 + x_1y_2+x_2y_1$  $Y_2 = x_2+x_1y_1y_2 + x_1y_1$  $Z = x_2+y_1$ (i) Draw the logic diagram of the circuit. (ii) Derive the transition table and output map. 8,K2,CO1

- 12. a) In the design a network produces a 1 if and only if the current input <sup>13,K3,CO2</sup> and the previous 3 inputs correspond to either of the sequence 1001 or 0110. The one output occurs at the time of fourth input of the recognized sequence. Output of 0 is to be produced at all other times and the sequences are allowed to overlap. Give the state diagram and the reduced state table.

## OR

- b) Design a 0110/1001 sequence detector. Give the state diagram and the 13, K3, CO2 reduced state table.

- 13. a) Derive the primitive flow table and state Diagram for the system with <sup>13,K2,CO3</sup> inputs X and Y and output Z. Initially both inputs and outputs are 0. If X = 1 and Y = 0 output Z=1. When X = 0 and Y = 1 output Z=0.If X = Y = 0 or X = Y = 1 then output Z has no change. The logic system has edge triggered input and any static inputs will not have any effect on the system output Z.

## OR

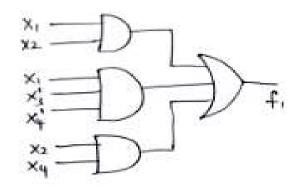

b) For a given diagram, find a-test using kohavi algorithm to find faults in 13, K2, CO3 x1.

14. a) Discuss in detail the interconnects and memory architecture of Xilinx <sup>13,K2,CO4</sup> 2000 with necessary diagram.

#### OR

- b) Explain in detail the Programmable Electrically Erasable Logic and the <sup>13,K2,CO4</sup> different Programming Techniques.

- 15. a) A combinational logic circuit is defined by the function given below. <sup>13,K2,CO5</sup> Implement the circuit using Programmable Array Logic.  $F(R,S,T,U) = \sum(3,5,7,14,15)$  $G(R,S,T,U) = \sum(3,4,5,7,10)$ OR

- b) Implement the following Boolean function using Programmable Logic 13,K2,CO5 Array.

$W(A, B, C, D) = \sum (0,2,6,7,8,9,12,13)$   $X(A, B, C, D) = \sum (0,2,6,7,8,9,12,13,14)$   $Y(A, B, C, D) = \sum (2,3,8,9,10,12,13)$  $Z(A, B, C, D) = \sum (1,3,4,6,9,12,14)$

### PART - C $(1 \times 15 = 15 \text{ Marks})$

16. a) Analyze the operation of 4:1 Multiplexer and compare the VHDL *15,K4,CO6* programming model of the same.

#### OR

b) Compare and contrast the structural and behavioral modeling of VHDL <sup>15,K4,CO6</sup> with suitable examples.